**MARCH** 2013

www.edn-europe.com Issue 3

# europe

Low-cost embedded graphics

Page 4

Page 16

Common inter-IC digital interfaces for audio data transfer

Page 34

Detecting and distinguishing cardiac-pacing artifacts

Page 28

Why your 4.7-µF ceramic cap becomes a 0.33-µF cap Page 23

### contents

**March 2013**

# 16 Signal integrity issues on the rise EDN collates the opinions of a "virtual panel" who offer eye-opening advice for anticipating, detecting, and mitigating SI problems in faster, increasingly complex designs. Moderated by Janine Love, Editor in Chief, Test & Measurement World

### 23 Why your 4.7-μF ceramic cap becomes a 0.33-μF cap

An investigation into temperature and voltage variations in X7R capacitors underscores the importance of data sheets.

By Mark Fortunato, Maxim Integrated

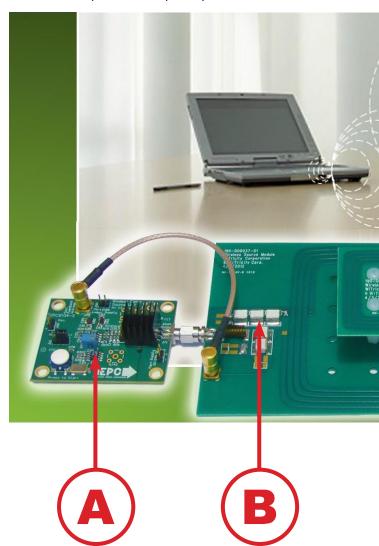

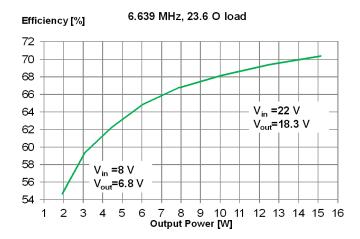

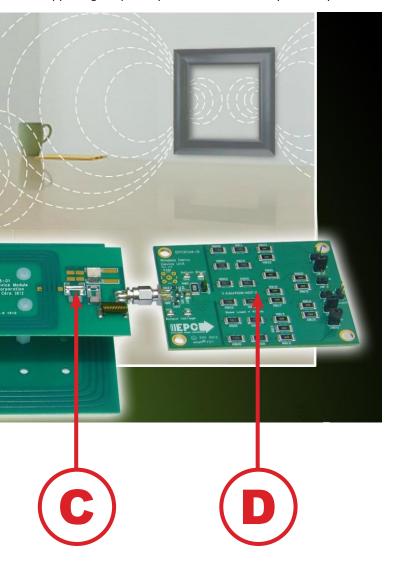

### 26 Anatomy of a highly-resonant wireless power transfer system

Efficient Power Conversion (EPC) made available a demonstration board, or more correctly a suite of boards, that act as a demonstrator and development tool for a wireless power transfer scheme.

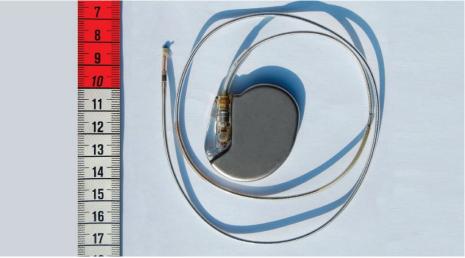

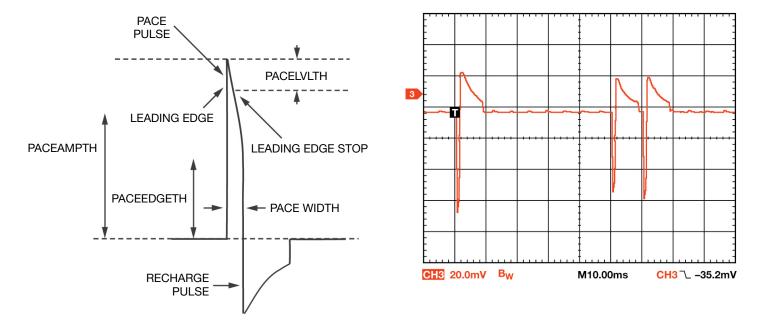

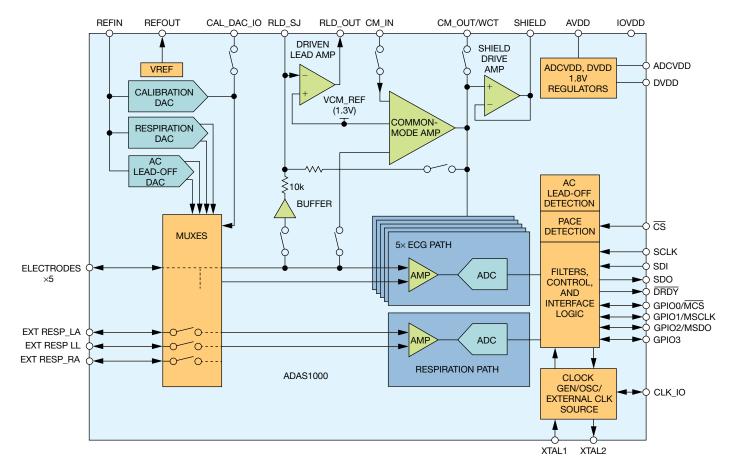

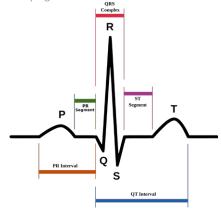

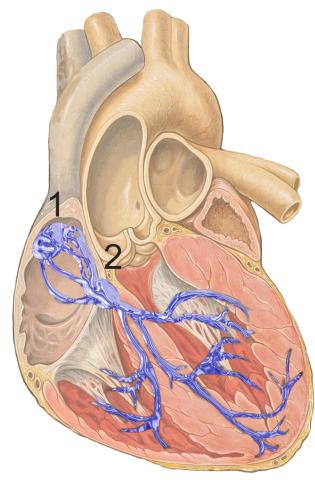

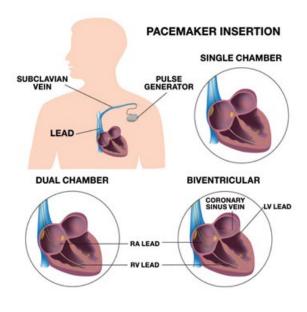

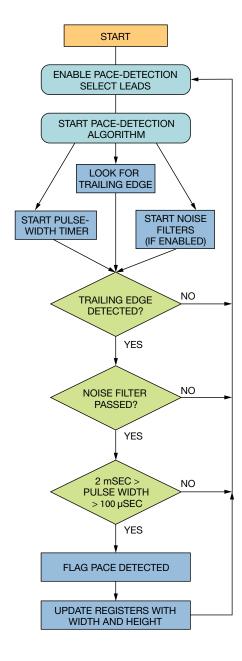

### 28 Detecting and distinguishing cardiacpacing artifacts

Buried in noise and larger cardiac signals, the artifacts of a pacemaker are difficult to spot. A combination of signal processing and methodology can help interpretation. By John Kruse and Catherine Redmond, Analog Devices

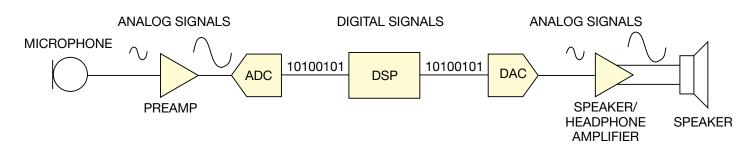

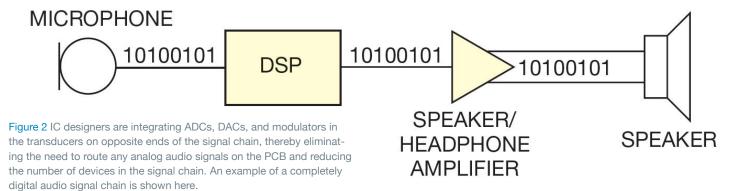

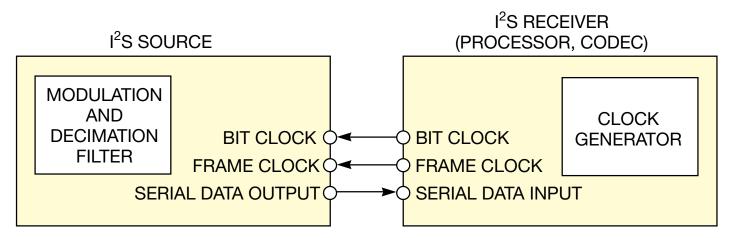

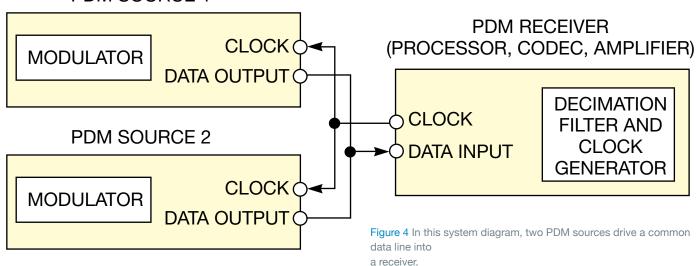

### 34 Common inter-IC digital interfaces for audio data transfer

Understanding the pros and cons of different interfaces before selecting parts helps ensure that you have the most efficient implementation of the signal chain. By Jerad Lewis, Analog Devices

### **DEPARTMENTS & COLUMNS**

### 7 EDN.comment

Battery management matters

### 14 Baker's Best

What does "rail to rail" output operation really mean?

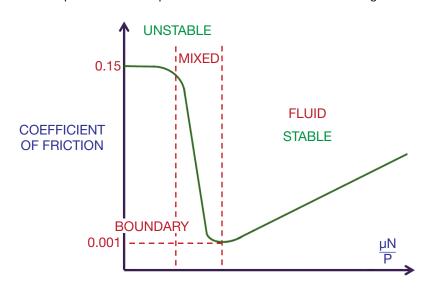

### 41 Mechatronics

Tribology – an essential but neglected science

### 44 Tales from the Cube

Nonlinear transmission lines keep developer on the fence

### **42** Product Roundup

### **DESIGNIDEAS**

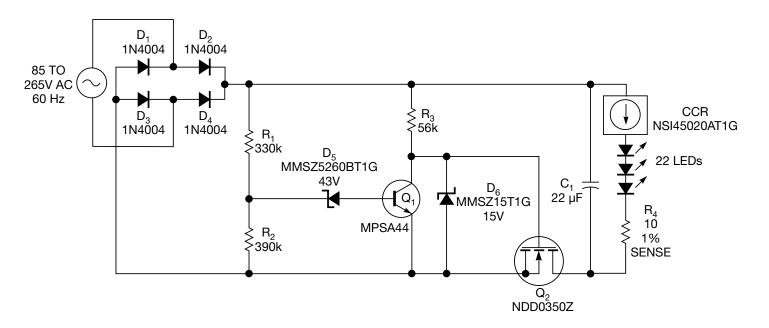

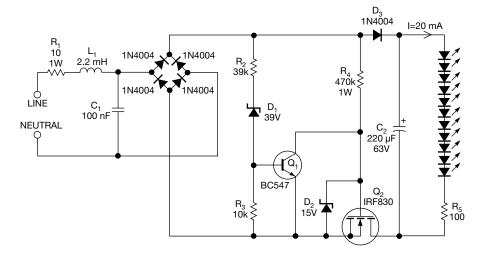

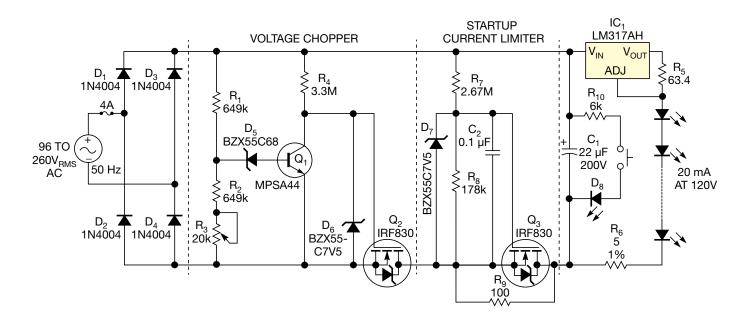

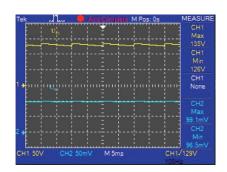

- 37 An improved offline driver lights an LED string

- 39 Low-duty-cycle LED flasher keeps power draw at 4 mW

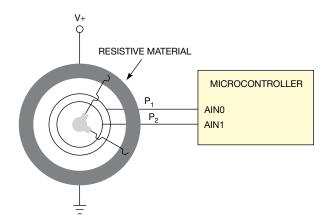

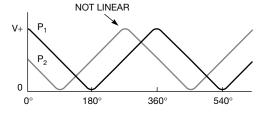

- 40 Rotary encoder with absolute readout offers high resolution and low cost

### pulse

- 4 Graphics controller cuts cost of embedded displays

- 8 Microchip turns tag into touch

- 10 Tanner offers open-access for EDA tool suite

- 10 Open source RF hardware for wireless innovation

- 11 Multi-cell balancing to increase battery pack performance

- 12 Smallest ARM-based MCU, claims Freescale

- 13 Intel steps up support for industrial control designs

- 13 Design RS485 links with assured EMC protection

### StrongIRFET™ Rugged, Reliable MOSFETs

### **Specifications**

| Part Number    | B <sub>vdss</sub> | ID@<br>25°C | R <sub>DS(on)</sub> max@<br>Vgs = 10V | Qg@<br>Vgs = 10V | Package                 |  |

|----------------|-------------------|-------------|---------------------------------------|------------------|-------------------------|--|

| IRFH7004TRPbF  | 40 V              | 100 A       | 1.4 mΩ                                | 134 nC           | PQFN 5x6                |  |

| IRFH7440TRPbF  | 40 V              | 85 A        | 2.4 mΩ                                | 92 nC            | PQFN 5x6                |  |

| IRFH7446TRPbF  | 40 V              | 85 A        | 3.3 mΩ                                | 65 nC            | PQFN 5x6                |  |

| IRF7946TRPbF   | 40 V              | 90 A        | 1.4 mΩ                                | 141 nC           | DirectFET<br>Medium Can |  |

| IRFS7437TRLPbF | 40 V              | 195 A       | 1.8 mΩ                                | 150 nC           | D²-Pak                  |  |

| IRFS7440TRLPbF | 40 V              | 120 A       | 2.8 mΩ                                | 90 nC            | D²-Pak                  |  |

| IRFS7437TRL7PP | 40 V              | 195 A       | 1.5 mΩ                                | 150 nC           | D²-Pak 7pin             |  |

| IRFR7440TRPbF  | 40 V              | 90 A        | 2.5 mΩ                                | 89 nC            | D-Pak                   |  |

| IRFB7430PbF    | 40 V              | 195 A       | 1.3 mΩ                                | 300 nC           | T0-220AB                |  |

| IRFB7434PbF    | 40 V              | 195 A       | 1.6 mΩ                                | 216 nC           | T0-220AB                |  |

| IRFB7437PbF    | 40 V              | 195 A       | 2 mΩ                                  | 150 nC           | T0-220AB                |  |

| IRFB7440PbF    | 40 V              | 120 A       | 2.5 mΩ                                | 90 nC            | T0-220AB                |  |

| IRFB7446PbF    | 40 V              | 118 A       | $3.3~\mathrm{m}\Omega$                | 62 nC            | T0-220AB                |  |

| IRFP7430PbF    | 40 V              | 195 A       | 1.3 mΩ                                | 300 nC           | T0-247                  |  |

For more information call +49 (0) 6102 884 311

or visit us at www.irf.com

### Features:

- Ultra low R<sub>DS(on)</sub>

- High current capability

- Industrial qualified

- Broad portfolio offering

### **Applications:**

- Battery Packs

- Inverters

- UPS

- Solar Inverter

- DC Motors

- ORing or Hotswap

[www.edn-europe.com] MARCH 2013 | EDN Europe 3

### Graphics controller cuts cost of embedded displays

Previously known for its range of USB interface chips, FTDI Chip has diversified into the display-controller market with its Embedded Video Engine (EVE), FT800. The company has applied the same principles to the display sector as it did to USB, according to founder Fred Dart; it has packaged up in an easy-to-use form, all of the functions necessary to implement a small display panel, with resistive touch, and has enabled a significant reduction in cost. With the chip at \$2.75 (100,000) and a \$9 display, you might build in a complete, small, intelligent display for around \$15-\$17. Dart outlines how, by devising a display controller entirely programmed using object-oriented techniques, expensive elements normally found in a display system, such as a frame buffer, have been eliminated.

With the FT800, and driving it from a simple microcontroller, you can add an intelligent QVGA or WQVGA TFT display panels to a design. The object oriented approach renders images in a line by line fashion with 1/16th of a pixel resolution. It supports 4-wire resistive touch sensing with built-in intelligent touch detection and an embedded audio processor allowing midi-like sounds combined with pulse code modulation (PCM) for audio playback. The object orientated approach means objects such as images, fonts and audio elements can be easily implemented and manipulated via a low pin-count SPI or I²C interface. In order for the desired GUI to be realised, you initialise the object memory (up to 256 kBytes) and then control the specified objects and their attributes through construction and interaction of a small display list buffer. As a result of this, even low end (8-bit) MCUs can be used as the host. Up to 2000 objects can be controlled within an 8k byte display list.

The FT800Q is capable of providing 24-bit (true colour) support on an 18-bit interface. It comes preloaded with a useful set of fonts and sounds on its ROM: anti-aliasing mechanisms improve the appearance of the display's output when rendering lines and complex shapes or when implementing signatures on resistive touch screens: in everyday terminology, eliminating "jaggies". Built-in widgets mean that even complex objects (such as analogue clocks) can be implemented with a high quality image. The embedded video engine uses a 36-stage pipeline, with odd/even line buffering. The chip uses 35 mA (typical) in active mode and 25  $\mu$ A in sleep mode. It has a -40 to 85°C operational temperature range and is packaged in a 7 x 7 x 0.9 mm 48-lead VQFN package. Dart adds, "With EVE, we are redefining the cost/quality paradigm for GUI development and offering intelligent display solutions with far more competitive price points... for [applications such as] point of sale equipment and printers, while enabling colour touch screen functionality to be added to thermostats, power meters, toys and common home appliances." - by Graham Prophet

FTDT chip, www.ftdichip.com/EVE.htm

### **Microchip**

### Power your most demanding setups with ease.

### No matter your application, accelerate with Agilent.

Whether it's automotive ECU, military communications, base station power amplifiers or general purpose test, maximize manufacturing throughput and

### **Agilent N6700 Modular Power System**

- 4 mainframes-manufacturing or R&D

- · 34 modules from 20 to 500 W

- 4 performance levels—basic to precision

R&D productivity. With seven new high-power modules from 300 to 500 W, Agilent helps you execute a wide range of high-power setups with the performance to measure milliamps accurately, too.

Agilent and our Distributor Network

Right Instrument. Right Expertise. Delivered Right Now.

www.rs-components.com/agilent

Download the new N6700 Modular Power System brochure

www.agilent.com/find/N6700PowerWW

© Agilent Technologies, Inc. 2012

Anticipate \_\_\_Accelerate \_\_\_Achieve

### FIND IT. DESIGN IT. BUY IT.

### **MARCH** 2013

www.edn-europe.com Issue 3

## europe

### **CONTACTS**

### **PUBLISHER** André Rousselot

+32 27400053 andre.rousselot@eetimes.be

### **EDITOR-IN-CHIEF**Graham Prophet

+44 7733 457432 gprophet@reedbusiness.fr

### **Patrick Mannion**

Brand Director EDN Worldwide

### CIRCULATION & FINANCE

**Luc Desimpel**

### luc.desimpel@eetimes.be

### ADVERTISING PRODUCTION & REPRINTS

Lydia Gijsegom

lydia.gijsegom@eetimes.be

### **ART MANAGER**

**Jean-Paul Speliers**

### ACCOUNTING

**Ricardo Pinto Ferreira**

### **EUROPEAN BUSINESS PRESS SA**

7 Avenue Reine Astrid 1310 La Hulpe

Tel: +32 (0)2 740 00 50 Fax: +32 (0)2 740 00 59 www.electronics-eetimes.com VAT Registration: BE 461.357.437

RPM: Brussels

Company Number: 0461357437

© 2013 E.B.P. SA

### EDN-EUROPE is published 11 times in 2013 by European Business Press SA, 7 Avenue Reine Astrid, 1310 La Hulpe, Belgium Tel: +32-2-740 00 50 Fax: +32-2-740 00 59

email: info@eetimes.be. VAT Registration: BE 461.357.437. RPM: Nivelles. Volume 15, Issue 2 EE Times P 304128 It is is free to qualified engineers and managers involved in

engineering decisions - see:

european

business press

http://www.edn-europe.com/subscribe Copyright 2013 by European Business Press SA.

All rights reserved. P 304128

### SALES CONTACTS

### **Europe**

### Daniel Cardon France, Spain, Portugal

+33 688 27 06 35 cardon.d@gmail.com

### Nadia Liefsoens Belgium

+32-11-224 397 n.liefsoens@fivemedia.be

### Nick Walker UK, Ireland, Israel, The Netherlands

+44 (0) 1442 864191 nickjwalker@btinternet.com

### Victoria & Norbert Hufmann Germany PLZ 0-3, 60-65, 8-9, Austria, Eastern Europe

+49 911 93 97 64 42 sales@hufmann.info

### Armin Wezel Germany PLZ 4-5

+49 (0) 30 37445104 armin@eurokom-media.de

### Ralf Stegmann Germany PLZ 66-69, 7

+49 7131 9234-0 r.stegmann@x-media.net

### Monika Ailinger Switzerland

+41-41-850 4424 m.ailinger@marcomedia.ch

### Ferruccio Silvera Italy

+39-02-284 6716 info@silvera.it

### Colm Barry & Jeff Draycott Scandinavia

+46-40-41 41 78

jeff.draycott@womp-int.com colm.barry@telia.com

### **USA & Canada**

### Todd A. Bria West

+1 831 477 2075 tbria@globalmediasales.com

### Jim Lees PA. NJ & NY

+1-610-626 0540 iim@leesmedia.com

### Steve Priessman East, Midwest, South Central & Canada

+1-630-420 8744 steve@stevenpriessman.com

### Lesley Harmoning East, Midwest, South Central & Canada

+1-218.686.6438 lesleyharmoning@gmail.com

### Asia

### Masaya Ishida Japan

+81-3-6824-9386 Mlshida@mx.itmedia.co.jp

### Bennie Hui Asian Sources Publications Hong Kong

+852 2831 2775

bennie@globalsources.com

### EDN.COMMENT

### **Battery management matters**

There's an old joke about the difference between hardware and software engineers that tells of three engineers in a car that suffers brake failure at the top of a hill. They arrive shaken but unhurt at the bottom of the hill; the hardware engineer wants dismantle the braking system and mend it; there's a project engineer in the car and he wants to set a project framework with a scheduled time-to-fix; and there's a software engineer who want to push the car back to the top to see if it does the same again. It's somewhat tempting to see something of the latter approach in Boeing's troubles with its lithium-ion battery packs, which are still causing all of the new 787s to be parked in corners of various airfields around the world. Meanwhile, Boeing is continuing to produce five new 787s each month, so the parking lot at Seattle must also be getting a bit crowded. At the time of writing this, Boeing (and its contractors) have proposed a solution to allow them to continue to use the same battery chemistry, and have applied to the Federal Aviation Authority to be allowed to flight-test it. The proposal, as far as details have been released, appears to involve placing a little more space and thermal isolation around each cell in the battery pack; enclosing it in a more fire-resistant enclosure; and arranging for that enclosure to be vented to the outside if things go wrong.

What does not seem to have been gained so far is any thorough understanding of why the battery packs in two aircraft suffered "severe overheating events". The history of lithium-chemistry battery development has been long, and a propensity to catch fire has had to be overcome at more than one stage along the way. I recall visiting a factory that was working on Li-ion technology very early, over 20 years ago. At that time the battery structures used much more metallic lithium: that factory was, literally, hard-wired to the local fire department. Later, we had the laptop-battery-fire episodes; and incidents of lithium batteries catching fire while being transported in bulk, while not even in-service. All of these, the battery technologists have overcome and in one view, Boeing's problems will be just one more step along that path. Reports on the incident on the apron at Boston say that the battery pack was not overcharged beyond its specification. However, it seems unlikely that the pack was at that stage monitored by the aircraft's data recorder down to the level of individual cells, and we know that cell-to-cell equalisation is very important in managing lithium-ion batteries - in fact, in the pages of this issue, you will find news of another novel chip designed to do exactly that. Boeing is opting to persist with taming the Li-ion technology: Airbus (in a not-exactly-equivalent application) has said it will take a step back to NiCd batteries, and accept the lower power density. Why, some commentators have asked, did Boeing select such a radically new (for a flight-critical system) battery technology? It's a question that does not stand scrutiny; in the course of the design, Boeing had to optimise the weight/ performance profile of every aspect of the 787: there would have been no more reason to leave the battery in an older technology than to have held back on, for example, the extensive use of composite materials in the airframe. In one sense, this is how engineering has always progressed, at its most fundamental level. Analysis is good when you can have it, but sometimes you have to resort to pushing the boundaries and experimenting. Build that arch a little higher, that bridge a little wider - if it falls down, you know your existing technology isn't up to the task, and more research is needed.

We may be sure that when Boeing resumes test flights, those battery packs will be instrumented in every conceivable parameter and, hopefully, will reveal exactly why the existing pack design failed the way it did. The least satisfactory outcome would be that one or more design changes cause the problem to go away, without revealing the fundamental reasons why the failures occurred. There are going to be many more high-density battery packs around us in the near future, and we need to understand them completely.

Meanwhile, it's down to Boeing to push the car back to the top of the hill – or in this case, get back up to 12,000m – and wait to see if it does it again.

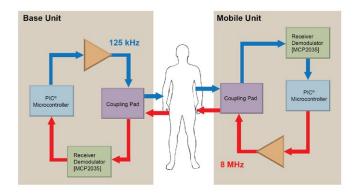

### Microchip turns tag into touch

BodyCom technology is a way of using the human body as a secure, low-power communication channel, according to Microchip Technology. Bodycom uses a small, low-power module which you carry on your person. It does not have to be in close contact with the body, carrying it in a pocket is sufficient: but once carried, it enables you to make a "touch" contact with the other part of the BodyCom, a transceiver IC, via an electrode array. By analogy with an NFC tag system, the portable unit turns the user's body into the tag, enabling a low-data-rate exchange (up to 10 kbit/sec) over a very short distance – a touch or proximity contact. You can use it to connect securely to a range of wireless applications, with bidirectional authentication for advanced encryption technologies. Applications can see extended battery life by

eliminating the need for a wireless transceiver or high-power inductive fields. No RF antennas are required, and BodyCom offers simple circuit-level design through use of the BodyCom Development V1.0 Framework, which is supplied through free software libraries that work on all of Microchip's PIC microcontrollers.

BodyCom technology is activated by capacitively coupling to the human body. The system then begins communicating bidirectionally between a centralised controller and one or more wireless units. You can use the scheme, Microchip suggests, as the basis of a highly-secure channel with bidirectional authentication supporting advanced encryption, such as KeeLoq technology and AES. BodyCom technology helps to prevent the "Relay Attack" problem that is typical in automotive passive-keyless-entry security systems, Microchip adds. The list of possible uses is long, but includes keyless entry; enabling or disabling potentially harmful devices such as power tools (the product will only power-up when held by an authorised user); a similar solution for weapons; medical devices; or consumer electronics such as profile management for gaming consoles and exercise equipment. The "terminal"

side of the transaction needs only to be equipped with a conductive array that can be touched by the user, similar to any touch-enabled device. The array can be shared with other touch applications; and transparent ITO (indium-tin-oxide) conductors work well. Therefore, any touch-screen device might have authentication added and would only respond to users who themselves carry a validating tag.

Signals are conducted over the body (from touching finger to pocketed tag) at, Microchip says, picoAmp levels; antenna design is unnecessary, as the systems uses a low-frequency framework with a common microcontroller and standard AFE frequencies (125 kHz and 8 MHz), with no need for external crystals. BodyCom technology also eliminates the cost and complexity of certification because it complies with FCC Part 15-B for radiated emissions.

More at www.microchip.com/get/GA5E

### Digitally enhanced power control

Also recently new from Microchip is its digitally enhanced power analogue controller for DC/DC designs – an analogue-based power management controller with integrated MCU, for flexible power conversion; with matching 25-V MOSFETs. Designers of power conversion products who would like to gain the benefits – or at least, some of the benefits – of digital power techniques, without committing themselves to a full-scale digital power design exercise, are offered Microchip's MCP19111. The part marries – on a single die – an analogue power regulator controller, along with a flash-based 8bit PIC microcontroller that carries out configuration, supervisory, reporting and control functions. The part operates from 4.5 to 32V.

Microchip notes that many companies are reluctant to switch to digital power - that is, full digital power designs, where the regulatory control loop is carried out in the digital domain - because of the resource implications of requiring digital design techniques from groups who may not have that expertise. Microchip's solution is to combine its analogue and logic circuitry experience in a single chip; the analogue portion comprises a peak-current regulator controller that drives external MOSFETs via a PWM (pulse-width modulation) generator. Key parameters that, in a fully-analogue part, would be set by external passive components, are controlled by selected values from on-chip switched-arrays of resistors and capacitors. Making that selection is firmware that runs on the associated 8-bit MCU core. The firmware comes with the part, and you set it up via a GUI; no programming is needed. The MCU core has multiple connections into the analogue control loop and can report key voltage and current level, set and monitor thresholds, and report faults over a serial connection. You do not have to write code for the MCU core, but there is capacity to run code if you choose to do so; a Microchip spokesman says that once the power-up configuration is done. the core "has not got much to do" - the computation load that would occupy a DSP or MCU core in a digital part is largely

embodied in the analogue loop – and perhaps only 25% of the capacity of the core might be taken up. If you add a PMBus protocol stack to communicate with the digital power bus, that might use 50% of the core's time; but there would still be the capability to implement, for example, a watchdog routine. There is, however, no facility (or the computational resource) to carry out an auto-compensation routine; as is normal for an analogue regulator, the designer will have to establish the correct loop compensation to achieve stable and responsive behaviour. Once the correct loop filter values have been determined, however, the on-chip microcontroller selects the appropriate R and C values from on-chip arrays: no external parts are needed, and the same base part can be set up with many different values for different applications.

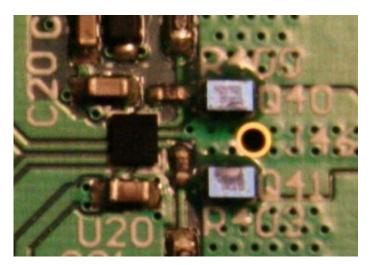

Microchip has been developing its own power output FETs and has released new parts to accompany the 19111 - although the part will drive FETs from other sources. MCP87018, MCP87030, MCP87090 and MCP87130 are high-speed 1.8 m $\Omega$ , 3 m $\Omega$ , 9  $m\Omega$  and 13  $m\Omega$  logic-level MOSFETs rated at 25V. Microchip claims a very low (good) figure-of-merit of on-resistance-timesgate-charge; the company notes that, with both controller and MOSFET technology in-house, higher-integration solutions such as multi-FET arrays on a single substrate are a possibility, and Microchip's designers will explore such options as market need dictates. An MCP19111 Evaluation Board (ADM00397) is priced at \$49.99 and also includes Microchip's high-speed MOSFETs. It comes with standard firmware, which is user-configurable through an MPLAB X IDE Graphical User Interface (GUI) plug-in. The MCP19111 will cost \$2.81 (5000); volume pricing for the FETs ranges from \$0.29 to \$1.04. - by Graham Prophet Microchip.

www.microchip.com/MCP19111

### Tanner offers open-access for EDA tool suite

Tanner EDA, popular as a layout and verification tool set among chip designers of medium-scale, mixed signal ASSPs and ASICs, has released version 16 of its HiPer Silicon full-flow design suite, offering designers a complete analogue and mixed-signal design flow from digital (HDL) and analogue (Spice, Verilog-A) electrical design and simulation, through synthesis to physical layout and verification.

Among the changes that Tanner is offering with this release is the OpenAccess database, which the company regards as "[a] most significant development in the semiconductor design tools market".

The objective is to enable customers to use Tanner tools, or any other provider's tool, at any point in the design flow – to step in and out of the the tool chain – with complete tool interoperability while maintaining data in the single database: and to bring a new degree of flexibility and accuracy to process design kits (PDKs) from a variety of silicon foundries. Interoperable PDKs should be usable, Tanner says, with any software flows and with the same common database. Acknowledging that foundries will verify their PDKs against the tool sets of the biggest companies in the sector, Tanner was faced with the task of having its tools interpret all aspects of the design data in the same way. Some of this was specified,

the company says, and some had to found by trial-and-error, a lengthy process.

Partly as a consequence of this progress towards an openaccess model, version 16 now permits a much higher degree of collaborative and distributed design activity, with team members able to work on the same database with greater ease. Tanner has also added a "traditional" logic design flow to its AMS (analogue/mixed-signal) offering, with HDL through synthesis to layout; synthesis has come from Incentia, and a digital simulator from Aldec has been added. Other enhancements in v16 include; new capabilities for back-end (layout); improved file loading and rendering speeds; improved physical verification (HiPer Verify); new capabilities for front-end (schematic capture, simulation, waveform viewing); integrated mixed-signal simulation (Verilog-AMS co-simulation); plus parametric plots, scatter plots and improved text control and graphics manipulation. - by Graham Prophet

Tanner EDA, www.tannereda.com

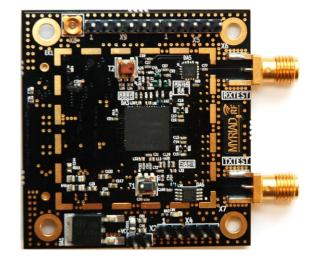

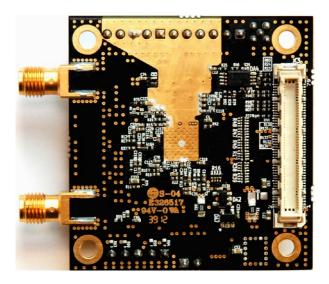

### Open source RF hardware for wireless innovation

By analogy with the innovation spurred by open-source exemplars such as Linux, and by hardware standards such as Arduino, Lime Microsystems aims to drive innovation in use of the RF spectrum by launching an open-source RF initiative: the non-profit organisation is initially based around a low cost, easy to use, fully configurable RF platform with pre-made boards and free, open, editable design files.

Myriad-RF is a website, aspiring to become an on-line community, that aims to give both experienced design engineers and hobbyists a range of low-cost RF boards and free design files available for general use. Future board designs will come from the wider Myriad-RF community, with the first board (Myriad-RF 1) designed by Taiwanese distributor Azio Electronics.

Lime markets highly integrated, single chip programmable transceivers, that you can set up to work in any one of a wide span of RF bands, with multiple modulation schemes, and with any suitable baseband signalling. In effect, its product is a software-defined-radio-on-a-chip. Its first product (LMS6002D) reached production in late 2010 and the company claims a

### pulse

customer base of around 150, with several product designs having reached production. These are typically from sectors such as small-cell basestation makers, where experienced RF designers were among the first to exploit the chip's capabilities. However, Ebrahim Busherhi, Lime CEO and instigator of Myriad-RF, believes that the ease-of-use of configurable RF technology should be a platform on which a diverse array of new product concepts can emerge, and that the open community approach may be the way to further that aim. Myriad-RF boards use field programmable RF (FP-RF) transceivers to operate on all mobile broadband standards - LTE, HSPA+, CDMA, 2G - including all regional variants; and any wireless communications frequency between 0.3 and 3.8GHz. This includes the regulated, licensed bands and unlicensed/whitespace spectra. Lime has also beta-launched the Myriad-RF community website and forum, www.myriadrf. org. This resource will also house the board design files and example projects with how-to guides and the ability for users to contribute extra content. All of the design files will be open and downloadable - the CAD environment is KiCad (www.kicadpcb.org).

Designs hosted on myriadrf.org will initially come from Lime and close partners, but Lime seeks to increase involvement and design contribution from the general RF design community both hobbyists and professional system designers. Azio's Myriad-RF 1 board measures approximately 5x5cm, uses a 5V power supply and is software configurable to operate from 300MHz to 3.8GHz and on 2G, 3G and 4G communication networks. Pre-built boards will initially retail for \$299 or less: Busherhi hopes this will reduce over time. A distribution network is already in place for pre-built boards and components with Azio Electronics and Eastel already participating. Links to all available pre-built boards can be found on the Myriad-RF board pages. Busherhi mentions ideas such as the possibility of using an FPGA-based baseband board together with a Myriad-RF card, which would provide an environment that would be totally programmable from one end of the signal chain to the other. The Myriad board is, he says, "a simple board with simple connections - you don't have to worry about the RF, it becomes part of the design."

Although Lime Microsystems has an established customer base in areas such as military radio and defence, and in cellular basestations, Busherhi is emphatic that he does not want to restrict activities to any niche sectors; "When we got (our chip) in production, we went broad-market right away, selling it in any quantity to any customer." With Myriad-RF, he hopes to expand that base in the open model. - by Graham Prophet Lime Microsystems, www.limemicro.com

# Multi-cell balancing to increase battery pack performance

Linear Technology's LTC3300-1 is the company's latest IC that addresses the problem of managing the state-of-charge of a multi-cell battery, such as the battery packs in electric vehicles or hybrids (Evs/HEVs). The underlying problem is that cells are never identical and as they age, capacities degrade, and by different amounts in different cells. Unless managed, the capacity of the pack is set by the performance of the lowest-capacity cell. Linear's latest chip balances the cell state of charge in a series-connected battery stack. Many existing solutions carry out balancing by reducing the charge

on higher-charged cells to match the lowest; this optimises the performance of the pack but is inefficient, as the marginal energy is dumped in resistive discharge. LTC3300-1 goes beyond dissipative passive balancing solutions, efficiently transferring charge to or from adjacent cells in order to bring mismatched cells into balance within the stack. Benefits claimed are faster charging and extending the run time and usable lifetime of the battery stack.

You would use the LTC3300-1 in a battery management system (BMS) for series-connected Li-lon or LiFePO4 batteries. Proposed architectures for active cell balancing include switched circuit arrangements with capacitive or inductive elements, in which some energy is taken from the highest-level cell and passed along the series-connected chain to the lowest. This needs many conversion steps to move a significant amount of charge. Or, there are single-transformer approaches in which the entire pack is switched across, in effect, the primary of a transformer, and the secondary is selectively connected back to the weakest cell. This also requires long balancing times.

[www.edn-europe.com] MARCH 2013 | EDN Europe 11

Linear's approach is to use a small transformer per cell with the IC acting as a fault-protected controller IC for transformerbased bidirectional active balancing. The part uses a nonisolated bidirectional synchronous flyback topology to balance up to six series-connected cells. Charge can be transferred to or from a selected cell and 12 or more adjacent cells. All balancers can operate independently and simultaneously with charge/discharge currents up to 10A. Bidirectional operation and simultaneous balancing minimises the time required to equalise the stae-of-charge in the stack, and the parts' high transfer efficiency (up to 92%) enables high current balancing with minimal power dissipation.

You control each individual balancer via a level-shifting SPIcompatible serial interface which enables multiple LTC3300-1 devices to be connected in series, without optocouplers or isolators - this is an approach Linear has developed with previous cell-balancing ICs. Linear has, previously, introduced precision monitor ICs such as the LTC6803-1, that have the dynamic range to accurately measure the small increments that represent state-of-charge differences. The part's stackable architecture together with interleaved transformer connections enable efficient balancing of every cell in an arbitrarily long string of series-connected batteries, even at the level of packs with a voltage of over 1000V. The chip integrates all associated gate drive circuitry, precision current sensing, fault protection circuitry and serial data interface, together with watchdog timer and cyclic redundancy check (CRC) data error checking are integrated. It comes in thermally-enhanced surface-mount compatible packages: a low profile (0.75mm) 48-lead 7 x 7mm QFN and a 48-pin 7 x 7mm LQFP package. Operating junction temperature range is -40°C to +125°C and the part costs \$5.95 (1000).

www.linear.com/product/LTC3300-1

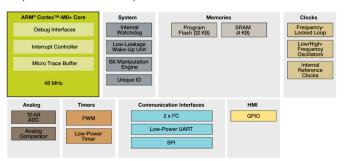

### Smallest ARM-based MCU, claims Freescale

Kinetis KL02, packaged in an outline of 1.9 x 2.0 mm lays claim to being the smallest-available microcontroller with an ARM core: Freescale intends that you use it in small, connected devices or the "Internet of Things" - or any space- and powerconstrained application. The chip hosts an ARM Cortex-M0+ processor, configured with analogue and communication peripherals. Small physical size is enabled by use of waferlevel chip-scale packaging (CSP) that connects the die directly to the solder ball interconnects and, in turn, to the PCB. This, Freescale observes, removes the need for bond wires

or interposer connections, reducing die-to-PCB inductance and improves thermal conduction and package durability for physically harsh environments. The KL02 device is the third CSP MCU in the Kinetis portfolio, joining the larger 120/143pin Kinetis K series K60/K61 variants. The KL02 sets a new minimum power level for the Kinetis family at 15.9 CM/mA; that is, the benchmark "CoreMark 1.0" rating - the conditions under which this was measured are profiled in the note below. Rated otherwise, Freescale puts the performance at 50 µA/MHz with a 4-µsec wake-up time.

Kinetis KL02 has sufficient processing power for complex algorithms, commuications stacks and human-interfaces, Freescale asserts: the chip also includes autonomous, poweraware peripherals (in this case, an ADC, UART and timer), 10 flexible power modes and extensive clock and power gating to minimise power loss. A low-power boot mode reduces power spikes during the boot sequence or deep sleep wake-up. This is useful, Freescale says, for systems in which battery chemistry limits the allowable peak current, such as those employing lithium-ion batteries frequently used in portable devices. Onchip is a 48-MHz ARM Cortex-M0+ core, operating over 1.71 to 3.6V; a bit manipulation engine for faster, more code-efficient bit-oriented mathematics; 32 KB of flash memory and 4 KB of RAM; a fast 12-bit ADC and a fast analogue comparator; and a range of low-power serial interfaces. There are also timers for applications including motor control.

You can develop systems on the "stackable" Freedom/Tower platform, with access to all of the usual sources of ARM code development tools. There is a software generation tool for creating device drivers and writing start-up code (Processor Expert/Solutions Advisor) and you can use Freescale's MQX real-time operating system.

Rated for operation over -40 to +85C, the chip begins sampling now and will be in production in July 2013: volume (100k) pricing is \$0.75.- by Graham Prophet

CoreMark 1.0 configuration: 108.69/IAR for ARM V6.50 --debug --endian=little --cpu=Cortex-M0 -e --fpu=None -Ohs --use c++\_inline/Code in internal FLASH, Data in internal RAM, Stack/ Processor operating frequency = 48MHz, operating voltage 3.0V Freescale, www.freescale.com/Kinetis/KL02CSP

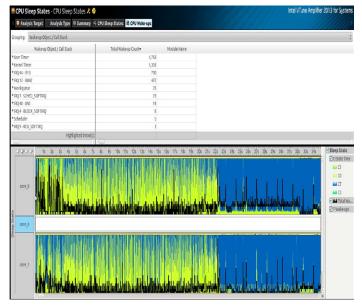

### Intel steps up support for industrial control designs

Intel has made a number of introductions around its Intelligent Systems Framework (ISF) including framework-ready products and two new software tools intended to support designers in the industrial market. One specific development is that of a PROFINET IO solution based on the Intel Ethernet Controller I210 and stacks from KW-Software, that achieves the highest level of PROFINET performance. The most common design practice has been to implement the PROFINET interface in an ASSP or an FPGA, Intel says; this development allows the

Intel's System Studio development environment generates a cycle-by-cycle plot of predicted power demand against program flow, to reveal where coding generates highest energy usage.

function to be brought into a standard chipset.

At the same time, Intel is releasing two new software tools – System Studio and the Firmware Support Package – to support ISF. System Studio integrates multiple development tools into a single package aimed at embedded and mobile software developers using Intel processors and SoCs. System Studio includes system and application debuggers, a memory and thread error checker and tools to optimise code for power efficiency (figure) and performance.

The Firmware Support Package provides low-level Intel CPU, Intel chipset and memory firmware initialisation capability using a standardised interface. Previous firmware solutions for embedded devices were, Intel says, highly customised and offered no backward compatibility: you can integrate the Firmware Support Package into any boot loader of the your choice, such as coreboot, Wind River VxWorks, BIOS, Real-Time Operating Systems, Linux and open source firmware. The Intel System Studio single user licence is available for \$3,499 and a floating license

(one seat) is available for \$5,299. The Firmware Support Package and the Intelligent

Systems Framework are available free of charge. - by Graham Prophet

Intel, www.intel.com

### Design RS485 links with assured EMC protection

Analog Devices has collaborated with Bourns - as a supplier of circuit protection devices - to offer what both companies claim is the first RS485 evaluation board with Certified RS-485 EMC performance. The challenge of matching the EMC characteristics of external protection devices and the components they are designed to protect is, ADI asserts, among the biggest contributors to schedule and cost overruns for manufacturers of industrial and instrumentation equipment. As the externally-certified, EMC-compliant design tool for RS-485 circuits, the EVAL-CN0313-SDPZ board provides design and integration files, device drivers, and evaluation hardware that you can import directly into a target project. The EVAL-CN0313-SDPZ also includes an El3 Hirose connector that allows the board to be used with ADI's ezLINX iCoupler Isolated Interface Development Environment, giving you a plug-andplay method to evaluate the digitally-isolated RS-485 physical communication layer.

The board incorporates ADI's ADM3485E, 3.3-V RS-485 transceiver and various circuit protection devices from Bourns and meets IEC61000-4-2/4/5 ESD (electro-static discharge), EFT (electronically-fast transients), and power-surge specifications. Specifically, the board offers line protection against 6-kV, 4-kV and 1-kV surges (IEC61000-4-5); 2-kV EFT and 8-kV contact (IEC61000-4-4); and 15-kV air-discharge ESD (IEC61000-4-2). It comes in ADI's "Circuits from the Lab" reference circuits library and includes circuit notes, test data and results that you can apply to applications such as motor controls, mains-connected inverters, and programmable-logic controllers. The development board will cost \$78: there will be a webcast on March 27th 2013, details at; www.analog.com/RS485EMC-Webcast

There is a video clip at; www.analog.com/RS485emc

- by Graham Prophet

Analog Devices, www.analog.com/RS485emc

BY BONNIE BAKER

### What does "rail to rail" output operation really mean?

he advertisements for single-supply operational amplifiers often claim rail-to-rail output capability. What does this assertion really mean? Page one of a single-supply op amp's data sheet may call out "rail-to-rail input/output swing" in the title or bullets; read on, because if you are looking for a single-supply amplifier whose output can be driven all the way to one supply rail and/or the other, good luck. So, what should you know about an amplifier's performance that claims rail-to-rail output operation?

Two amplifier specifications will help you sort out this problem: output-voltage swing and open-loop voltage gain.

The output-voltage swing of an op amp defines how far you can drive the amplifier output toward the positive or negative supply rail. The output-voltage-swing high ( $V_{OH}$ ) and output-voltage-swing low ( $V_{OL}$ ) test conditions usually take the amplifier outside its linear region. The amplifier's open-loop-voltage-gain ( $A_{VOL}$ ) specification primarily is the ratio of the closed-loop, output-voltage change to the input-offset-voltage change, but it also

provides output-linearity hints in the test conditions.

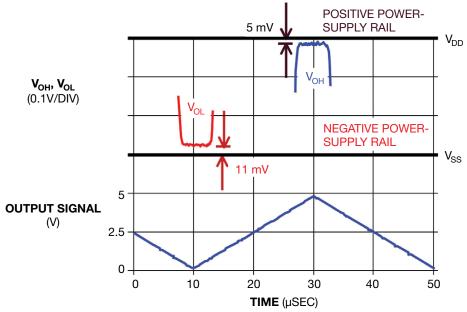

The  $V_{OH}$  and  $V_{OL}$  specifications tell us how close the output pin comes to the power-supply rails. Figure 1 shows a single-supply amplifier's output behavior. The output stage's transistors prevent the amplifier from reaching either rail.

As you examine these specifications with respect to their test conditions, you will find that the amplifier's output swing is dependent on the amount of current that the output stage is driving into the load. As you can see in Table 1 (Amplifier A),

viewable in the online version of this article at www.edn.com/4404550, the defined conditions of this specification have a significant influence on the amplifier's output performance. As the table shows,  $V_{OH}$  is the difference between  $V_{DD}$  (positive supply).  $V_{OL}$  is the difference between the minimum voltage out and  $V_{SS}$  (negative supply).

The key to comparing  $V_{\text{OH}}$  and  $V_{\text{OL}}$  from amplifier to amplifier is to determine the sink or source current. Smaller output currents provide better output-swing performance.

$V_{OH}$  and  $V_{OL}$  tell us how close the amplifier drives to the rails but do not imply that the amplifier is linear so close to the supply voltage rails; the conditions of the  $A_{VOL}$  specification, by contrast, do. Measure  $A_{VOL}$  by comparing the amplifier's output swing in its linear region with the amplifier's input offset voltage. The dc open-loop gain is equal to the following equation:

$$A_{VOI} = 20 \log(\Delta V_{OUT}/\Delta V_{OS}),$$

where  $\Delta V_{\text{OUT}}$  is the dc change in output voltage and  $\Delta V_{\text{OS}}$  is the dc change in input offset voltage.

Table 2 (Amplifier B), also at www. edn.com/4404550, shows an example of the  $A_{\rm VOL}$  specifications and test conditions for a single-supply amplifier. In the condition column, note that the high and low output ranges of the amplifier are 5 mV from the power supplies. The  $A_{\rm VOL}$  specification verifies that the amplifier is in its linear region.

If you are looking at a single-supply op amp that's claimed to offer rail-to-rail operation, make sure you look deeper before using the product in your application. Consider the  $V_{OH}$ ,  $V_{OL}$ , and  $A_{VOL}$  specifications and conditions. Doing so will keep you from wasting your time and will ensure that you have the correct amplifier for your circuit.EDN

Figure 1 The output signal ramping from  $V_{SS}$  (GND) to the positive power supply ( $V_{DD}$ =5V) never reaches either rail. At ground, the amplifier stops at ~11 mV from the rail; at  $V_{DD}$ , the amplifier stops at ~5 mV from the rail.

### One Core – Countless Options

The RX Family provides a true microcontroller platform with a solution for every application. Based on the powerful RX 32-bit CPU core the RX Family provides 100s of devices with common peripherals and common tools.

### **RX Benefits**

- 32-bit CPU with DSP/FPU

- 100 MHz Flash with no wait

- 3.12 Coremark /MHz

- 32 kB 2 MB on Chip Flash

- 8 kB 128 kB on Chip SRAM

- 48 177 Pin Packages

- Ethernet, 3ch CAN, 2ch USB

- 12-bit and 24-bit ADC

- 150 μA / MHz Operation

- 0.9 µA RTC Mode

- Safety Feature

### **RX Applications**

- Consumer Appliances

- Entertainment System

- Meters (Gas/Power/Water)

- Industrial networks

- Gateways

- Power Meters

- Medical Systems

- Motor Controls

- Sensors

- White Goods

### **RX For You!**

Register now to qualify for a free of charge RX board at:

www.renesas.eu/rx600

www.renesas.eu/rx

# SIGNALINTEGRITY ISSUES ON THE RISE

JANINE LOVE • EDITOR IN CHIEF, TEST & MEASUREMENT WORLD

# OUR VIRTUAL PANEL SHARES EYE-OPENING ADVICE FOR ANTICIPATING, DETECTING, AND MITIGATING SI PROBLEMS IN FASTER, INCREASINGLY COMPLEX DESIGNS.

lectronics design trends that ratchet up design complexity and speed, such as the use of multiple high-speed buses, bring new signal-integrity challenges. With that in mind, EDN assembled a virtual panel of engineers working in signal integrity to examine the current impairments, assess how well the available test equipment is measuring up, and determine what we can do both short- and long-term to improve signal integrity. Admittedly, there are many things that can affect signal integrity (Reference 1); in this discussion, we focus primarily on crosstalk and EMI.

### WHAT'S THE PROBLEM?

Many a trained eye is focused on the effects of multiple high-speed buses on signal integrity and how to avoid the related problems.

Chris Loberg, senior technical marketing manager at Tektronix Inc, and Tim Caffee, vice president for design validation and test at Asset InterTech Inc, agree that shrinking operating margins on high-speed buses are contributing to the challenges.

"The design trend is faster serial speeds, above 10 Gbits/sec, with no new cost-effective architecture for improving signal-path accommodation of issues like EMI and crosstalk," Loberg observes. "So, signaling accommodations like equalization must be made to minimize EMI and crosstalk effects, enabling the receiver to accurately determine the serial-bus logic transition."

Loberg notes that interval times—the time between a transition to one or zero—are shrinking; as a result, in a traditional eye diagram used to evaluate transitions, EMI and crosstalk are "closing" the eye. Engineers can no longer effectively evaluate signal integrity, as crossing points and timing-integrity evaluations become much more challenging.

Caffee notes that with each successive generation of high-speed bus, operating margins are gradually shrinking as signal frequencies increase, enabling effects such as jitter, intersymbol interference (ISI), and crosstalk to "create havoc" on the signal integrity of high-speed SerDes and memory channels. Each new step to a higher speed and signaling frequency makes the bus more susceptible to distortions and anomalies that can effectively disrupt traffic and stall system throughput.

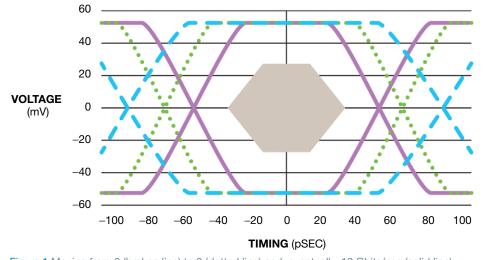

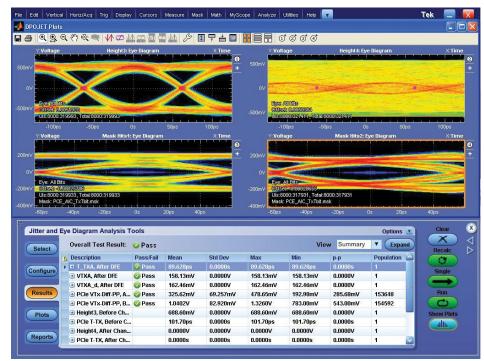

The eye diagram in Figure 1 illustrates this point, showing the effects of increasing signal frequencies on three generations of a hypothetical high-speed bus and the resultant, decreasing operating margins on the bus. As frequencies increase, even the slightest distortion can disrupt signaling throughput.

Alan Blankman, product manager for signal-integrity products at Teledyne LeCroy, agrees that higher bit rates (>25 Gbits/sec) and "parallelized serial" standards such as PCI Express (PCIe), 40/100GBase-R, and InfiniBand are contributing to signal-integrity issues. "Faster bit rates require faster edges with higher-frequency content, which results in bigger reflections due to impedance mismatches at connectors, vias, packages, etc.; higher levels of loss; and higher levels of crosstalk and EMI, due to increased coupling to neighboring traces," Blankman says.

Shamree Howard, signal-integrity program manager at Agilent Technologies, adds that faster speeds create issues for accurate data capture, requiring precise triggering. She says jitter measurements are the key to characterizing high-speed digital links, noting, "The measurement of jitter-even if the user is provided a one-button interface—is a sophisticated affair, taking into account clock recovery and knowledge of phase-locked loops, jitter decomposition techniques and assumptions for them, crosstalk and its effects, and waveform statistics that require different approaches" (Reference 2). Howard adds that the Agilent U4154A 4-Gbit/sec AXIe logic-analyzer module can make reliable measurements on eye

### AT A GLANCE

Each new step to a higher speed and signaling frequency makes the bus more susceptible to distortions and anomalies that can disrupt

traffic and stall system throughput. "Parallelized serial" standards are contributing to signal-integrity issues. Circuits at very high speeds are notoriously difficult to probe.

One way forward is to improve the signal path itself with an optical backplane; another way to improve signal integrity is to trick the signal using equalization approaches to minimize crosstalk.

Many designers are managing crosstalk and EMI through better design practices around the signal path.

Most engineers working on signal-integrity issues agree that simulation is becoming mandatory for high-speed system design.

openings as small as 100 psec  $\times$  100 mV (Figure 2).

Howard Johnson of Signal Consulting Inc concurs that circuits at very high speeds are notoriously difficult to probe. "Even in cases when a probe exists that can do the job, you often cannot place the probe at the point in a circuit that you wish to observe," says Johnson. He suggests that the answer is to use cosimulation, or the process of simultaneously developing both a physical circuit and a software simulation of it.

The problem, observes Ransom Stephens of Ransom's Notes, is that, despite new oscilloscope techniques from leading manufacturers, there is no automated way to identify crosstalk unambiguously. The latest test prod-

Figure 1 Moving from 6 (broken line) to 8 (dotted line) and, eventually, 10 Gbits/sec (solid line) closes the eye around the operational sweet spot at the center of the diagram (courtesy Asset InterTech).

ucts offer ways to estimate the effect of crosstalk on the bit error rate (BER), but they are all process-of-elimination approaches.

"Avoiding crosstalk is simple in principle but sometimes impossible in practice," Stephens acknowledges. Because crosstalk is caused by jolts of radiation when an aggressor signal makes a logic transition, increasing the rise/fall times will reduce crosstalk. Because it's interference, increasing trace separation has a big effect, too.

"I think that careful differential design is your best bet, though," Stephens offers. "If you can get the differential skew really small and get the two traces nearly on top of each other, then the cancellation from differential signaling has a fighting chance."

### **HOW DO WE IMPROVE SI?**

According to Tektronix's Loberg, there are several ways forward. First, change and improve the signal path itself. One way to do that is with an optical back-

# DESPITE NEW OSCILLOSCOPE TECHNIQUES, THERE IS NO AUTOMATED WAY TO IDENTIFY CROSSTALK UNAMBIGUOUSLY.

plane; this is happening, but not in the mainstream (think Thunderbolt). Another way to improve signal integrity is to trick the signal using equalization approaches to minimize crosstalk; for instance, you could hard-code the chip or compile FPGA code to equalize the signal. In addition, many designers are managing crosstalk and EMI through better design practices around the signal path.

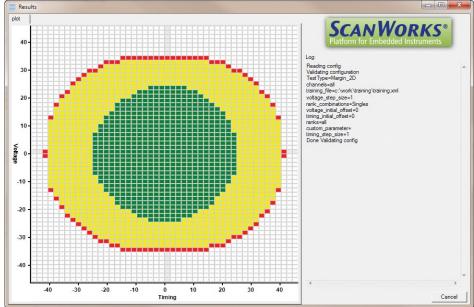

Asset InterTech's Caffee proposes that engineers validate signal integrity on the bus during each of the major phases of a system's life cycle, from design to field operation, though he recognizes that this is a challenging approach and thus not a popular one. If detected during prototype-board bring-up, signal-integrity problems could trigger changes in the design; if detected during manufacturing, problems could result in alterations to the production process. If problems are detected in the field as a result of troubleshooting poorly perform-

### Your question:

# Why full bandwidth up to 1 mV/div?

Our answer: For high signal fidelity and measurement accuracy on fast, low-amplitude signals.

The R&S®RTO oscilloscopes offer high vertical input sensitivity of up to 1 mV/div. They always operate at high measurement accuracy because the full bandwidth of the oscilloscope can be used at even the lowest sensitivity levels. Furthermore, the R&S®RTO oscilloscopes do not use software-based zooming. They show the signal's real test points at all sensitivity levels.

### Warranty program available until June 2013:

Register your new scope and get a five year warranty instead of three! www.scope-of-the-art.com/ad/warranty.

ing systems, design changes, manufacturing-process changes, or both should be made for the next product generation to reduce returns and warranty claims.

Hiroshi Goto, business development manager at Anritsu Co, suggests preemphasis as an effective transmission technique for maintaining the eye opening. With transmission speeds increasing to 20 Gbits/sec and faster, Goto proposes a three- or four-tap emphasis signal in order to increase the number of bits to be emphasized.

It's a complex job to check and set the combination of emphasis rates for each tap, however, making it difficult to find the ideal emphasis signal without quantitative guidelines.

The Anritsu-developed MP1825B four-tap emphasis and transmission-analysis software, working with the MP1800A signal-quality analyzer BER test set (BERTS), finds "the ideal emphasis settings based upon the reverse characteristics" of the device under test (DUT), says Goto (Figure 3). "This raises the height of the eye and keeps the eye open, allowing better quantitative signal-integrity analysis in the shortest amount of time."

### **SIMULATION AND VALIDATION**

Most agree that simulation is becoming mandatory for high-speed system design. Agilent's Howard says the company's Advanced Design System (ADS) is the leading EDA software in use for

Figure 2 The Agilent U4154A logic analyzer uses its eye-scan capability to place the sampling point automatically in both time and voltage within the eye, making measurements on eye openings as small as 100 psec × 100 mV.

Figure 3 The Anritsu MP1800A 32G synchronized multi-BERTS and MP1825B 28.1G four-tap emphasis aim to assist signal-integrity analysis by keeping the eye open.

high-speed digital applications.

Teledyne LeCroy's Blankman adds that to detect and mitigate crosstalk issues, designers must be able to predict near- and far-end crosstalk by running simulations, and to validate the models used in the simulations by taking measurements (Figure 4). To validate crosstalk models, designers need multidifferential-lane S-parameter measurements (eight-port for aggressor-victim models, 12-port for aggressor-victim-aggressor models, or even higher port counts).

Measuring crosstalk requires vertical noise measurements taken by real-time oscilloscopes that can extract the crosstalk from the serial data signal. Those measurements should estimate eye closure as a function of BER, as jitter measurements do. Jitter measurements are also important, of course. Measuring both jitter and noise yields a more complete picture of crosstalk than jitter mea-

surements alone.

### **TOOLBOX**

Test-equipment vendors are working to evolve their tools to characterize jitter and improve signal-integrity analysis, so the optimal toolbox for signal-integrity engineers may not yet be available. Signal Consulting's Johnson predicts that "the next trend will involve a blend of specialized equipment and test software designed to characterize a power system and inject specific test current waveforms into that power system." Stephens, of Ransom's Notes, suggests that we be on the lookout for more crosstalk-equalization techniques.

So, what's out there now?

• Scopes. Here is where high-band-width oscilloscopes can really prove their worth. Teledyne LeCroy's Blankman notes that nonreturn-to-zero (NRZ) serial data patterns can have rise times less than 30 psec. He points out that receiver testing of PCIe Gen3 systems requires a

Figure 4 The SPARQ signal-integrity network analyzers from Teledyne LeCroy connect directly to the DUT and PC-based software through a single USB connection for quick, multiport S-parameter measurements.

scope with a 13-GHz bandwidth, whereas transmitter testing needs a 20-GHz scope.

"Emerging multilane designs like InfiniBand and 40/100GBase-R have even more-demanding requirements for channel count and bandwidth," Blankman says. "These standards utilize bit rates of 25 and 28 Gbits/sec. Typically, an oscilloscope with four or five times the fundamental frequency is needed, which corresponds to 50 to 65 GHz. Since InfiniBand and 40/100GBase-R are multilane, acquiring eight, 12, or even more channels at a time is required to fully characterize SI issues." Blankman points to Teledyne LeCroy's LabMaster 10 Zi, with bandwidth out to 65 GHz and a ChannelSync architecture that synchronizes up to 80 channels to operate as a single instru-

• Network analyzers. Network analyzers are important for characterizing crosstalk in multilane systems and revealing the frequency characteristics of the DUT. Anritsu's Goto points out that in order to acquire the best S-parameter data, the vector network analyzer should have broad frequency coverage. He suggests Anritsu's VectorStar VNA, which ranges from 70 kHz to 125 GHz.

"While the upper frequency receives most of the attention," he warns, "it is important to remember that accurate measurements to the lowest possible frequency are critical for signal-integrity applications. Often, the accuracy of models can be improved by measuring down to as close to dc as possible, providing the precise data to help create a high-accuracy eye diagram."

Blankman notes that network analyzers with high port counts can be expensive. He says the network analyzers in Teledyne LeCroy's SPARQ series (Figure 4) were designed for signal-integrity measurements and offer a lower-cost option to a traditional VNA. (SPARQ stands for "S-parameters quick.")

• Software. Given the need for more simulation, vendors are developing software tools to work with their hardware. Loberg notes the availability of serial-data-link analysis (SDLA) on the Tektronix scope (Figure 5), which can help engineers simulate equalization in EDA environments such as those from Cadence Design Systems or Mentor Graphics. "That software model can be

Figure 5 This screen image of serial-data-link analysis shows different eye diagrams before and after inclusion of equalization effects and channel/fixturing effects (courtesy Tektronix).

dropped into an oscilloscope, transferring the model properties into the

JTAG PROVIDES

ACCESS TO AN EXTERNAL SOFTWARE-BASED

PLATFORM THAT CAN

MANAGE THE SYSTEM'S

EMBEDDED INSTRUMENTS.

S-parameters; then we can place the effects of that effort into a filter on the scope," Loberg explains. "The scope can then model the behavior of the equalizer into the signal being measured and see if we can open the eye. This approach allows you to analyze the performance with the effects of equalization baked into the scope."

Teledyne LeCroy also offers oscilloscope-based serial-data-analysis software in its SDAIII-CompleteLinQ product. Blankman notes that it is important to have scope-based software that performs eye, jitter, and vertical noise analysis. He says users also need tool kits that allow fixtures and interconnects to be de-embedded or emulated, and that apply transmitter and receiver equalization. "The analysis tool kit should also provide a wide variety of plots that show the variation and distribution of jitter and noise in frequency and time in order to understand the root causes of noise and iitter." Blankman adds.

• BERT. "Receiver testing is becoming mandatory in many standards, and most people don't know where to start," says Howard, who adds that system calibration—critical for ensuring the accuracy of your measurements—may be the hardest part of testing.

Howard reveals that in working with engineers, she has found proper calibration of the stress signal in PCle 3.0 to be challenging. She points to the Agilent N4903B J-BERT high-performance serial BERT to test Rx compliance. The instrument can characterize a receiver's jitter tolerance and is designed to prove compliance with today's most popular serial-bus standards, including PCle, SATA/SAS, DisplayPort, and USB.

Goto suggests that when selecting a BERT, engineers should choose one with minimal intrinsic jitter. For example, the Anritsu MP1800A has intrinsic clock jitter of <350 fsec RMS. The BERT should also be able to conduct repeatable and stable jitter-tolerance tests with a variety of generated jitter types, such as sinusoidal, random, and bounded uncorrelated jitter and spread-spectrum clock that can be measured up to 32.1 Gbits/sec.

• Embedded test. The days of probing test pads are coming to a close, especially for high-speed buses, because the practice can introduce anomalies into the signal. So where does

Figure 6 An eye diagram like this one can be generated by a tool set for embedded instrumentation (courtesy Asset InterTech).

that leave us? There is a growing interest in embedded test instruments, and the design-for-test movement is allowing nonintrusive embedded instruments to deliver the signal data that the receivers see. "In other words," says Caffee, "soft access is provided to the hard data that signal-integrity engineers need."

Embedded instruments have been used for years for chip-level characterization, verification, and test. But now, embedded instruments are being used to monitor and report data being received by the receiver. Caffee notes that the embedded instruments are accessed using standard technologies,

such as the IEEE 1149.1 boundary-scan (JTAG) test-access port.

"JTAG provides access to an external software-based platform that can manage the embedded instruments in the system, as well as compile and analyze the test and measurement data they gather," Caffee says (Figure 6).

As system speed and complexity continue to rise, the way forward looks to be a combination of advanced measurement tools and techniques that work with customized simulation models. In the end, though, the path of least resistance for improving signal integrity looks to be an industry standby: good old-fashioned engineering ingenuity.EDN

### **REFERENCES**

Bogatin, Eric, and Alan Blankman, "Use S-parameters to describe crosstalk," Test & Measurement World, Sept 13, 2012, www.tmworld.com/4396189. "Tips and Techniques for Accurate Characterization of 28 Gb/s Designs," Agilent Technologies, 2012, http://bit.ly/12m4lZ3

22 EDN Europe | MARCH 2013 [www.edn-europe.com]

# Why your 4.7-µF ceramic cap becomes a 0.33-µF cap

AN INVESTIGATION INTO TEMPERATURE AND VOLTAGE VARIATIONS IN X7R CAPACITORS UNDERSCORES THE IMPORTANCE OF DATA SHEETS.

few years ago, after more than 25 years of working with ceramic capacitors, I learned something new about them. I was working on an LED-light-bulb driver, and the time constant of an RC circuit in my project simply did not seem to be right.

I immediately assumed that there was an incorrect component value installed on the board, so I measured the two resistors serving as a voltage divider. They were just fine. I desoldered the capacitor from the board and measured that component; the cap, too, was fine. Just to be sure, I measured and installed new resistors and a new capacitor, fired up the circuit, checked that the basic operation was proper, and then went to see whether the component swap had resolved my RC time-constant problem. It had not.

### A TEMPERATURE PROBLEM?

I was testing the circuit in its natural environment: in its housing, which itself was in an enclosure to mimic a "can" for ceiling lighting. The component temperatures in some instances reached well over +100°C. Even in the short time it had taken me to retest the RC behavior, things had become quite hot.

My next conclusion, of course, was that the temperature variation of the capacitor was the issue. I was skeptical of that conclusion even as I drew it, however, because I was using X7R capacitors, which to my recollection varied only  $\pm 15\%$  up to  $\pm 125$ °C. I trusted my memory, but to be sure, I reviewed the

data sheet for the capacitor that I was using.

That is when my ceramic-capacitor reeducation began.

### **BACKGROUNDER**

Table 1 shows the letters and numbers used for various ceramic-capacitor types and what each means. The table describes Class II and Class III ceramics. Without getting too deep into details, Class I capacitors include the common COG (NPO) type; these are not as volumetrically efficient as the ones listed in the table, but they are far more stable over varying environmental conditions, and they do not exhibit piezo effects. The capacitors listed in the table, by contrast, can have widely varying characteristics; they will expand and contract with applied voltage, sometimes causing audible (buzzing or ringing) piezo effects.

Of the many capacitor types shown, the most common, in my experience, are X5R, X7R, and Y5V. I never use the Y5Vs, because they exhibit extremely large capacitance variation over the range of environmental conditions.

When capacitor companies develop products, they choose materials with characteristics that will enable the capacitors to operate within the specified variation (third character; Table 1) over the specified temperature range (first and second characters). The X7R capacitors that I was using should not have varied more than  $\pm 15\%$  over a temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C, so either I had a bad batch of capacitors or something else was happening in my circuit.

| TABLE 1 COMMON CERAMIC-CAPACITOR TYPES |                                                       |     |                     |                                         |            |  |

|----------------------------------------|-------------------------------------------------------|-----|---------------------|-----------------------------------------|------------|--|

| First ch                               | First character: low temp Second character: high temp |     | haracter: high temp | Third character: Change over temp (max) |            |  |

| Char                                   | Temp (°C)                                             | Num | Temp (°C)           | Char                                    | Change (%) |  |

| Z                                      | 10                                                    | 2   | 45                  | Α                                       | ±1         |  |

| Υ                                      | 30                                                    | 4   | 65                  | В                                       | ±1.5       |  |

| X                                      | 55                                                    | 5   | 85                  | С                                       | ±2.2       |  |

| -                                      | _                                                     | 6   | 105                 | D                                       | ±3.3       |  |

| _                                      | _                                                     | 7   | 125                 | Е                                       | ±4.7       |  |

| _                                      | _                                                     | 8   | 150                 | F                                       | ±7.5       |  |

| _                                      | _                                                     | 9   | 200                 | Р                                       | ±10        |  |

| -                                      | _                                                     | _   | _                   | R                                       | ±15        |  |

| _                                      | _                                                     | _   | _                   | S                                       | ±22        |  |

| -                                      | _                                                     | _   | _                   | Т                                       | 22, –33    |  |

| _                                      | _                                                     | _   | _                   | U                                       | 22, –56    |  |

| _                                      | _                                                     | _   | _                   | V                                       | 22, –82    |  |

### **NOT ALL X7Rs ARE CREATED EQUAL**

Since my RC time-constant problem was far greater than would be explained by the specified temperature variation, I had to dig deeper. Looking at the data for capacitance variation versus applied voltage for my capacitor, I was surprised to see how much the capacitance changed with the conditions I had set. I had chosen a 16V capacitor to operate with a 12V bias. The data sheet indicated that my 4.7- $\mu$ F capacitor would typically provide 1.5  $\mu$ F of capacitance under those conditions. Now, that explained the problem my RC circuit was having.

The data sheet then showed that if I just increased the size of my capacitor from the 0805 to the 1206 package size, the typical capacitance under the specified conditions would be  $3.4 \, \mu F$ . This called for more investigation.

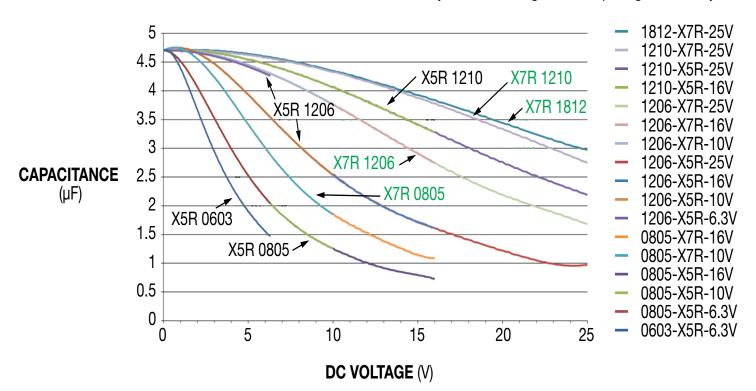

I discovered that Murata Manufacturing Co (www.murata. com) and TDK Corp (www.tdk.com) offer nifty tools on their Web sites that let you plot the variations of capacitors over different environmental conditions. I investigated 4.7-µF capacitors of various sizes and voltage ratings. Figure 1 graphs the data that I extracted from the Murata tool for several different 4.7-µF ceramic capacitors. I looked at both X5R and X7R types, in package sizes from 0603 to 1812 and with voltage ratings from 6.3 to 25V dc. Note, first, that as the package size increases, the capacitance variation with applied dc voltage decreases—and does so substantially.

A second interesting point is that, for a given package size and ceramic type, the capacitor voltage rating seems often to have no effect. I would have expected that using a 25V-rated capacitor at 12V would result in less variation than using a 16V-rated capacitor under the same bias. Looking at the traces for X5Rs in the 1206 package, it's clear that the 6.3V-rated part does indeed perform better than its siblings with higher voltage

| TABLE 2 CAPACITANCE OF X7R CAPS WITH A 12V BIAS |        |              |  |  |  |

|-------------------------------------------------|--------|--------------|--|--|--|

| Size                                            | C (μF) | % of Nominal |  |  |  |

| 0805                                            | 1.53   | 32.6         |  |  |  |

| 1206                                            | 3.43   | 73           |  |  |  |

| 1210                                            | 4.16   | 88.5         |  |  |  |

| 1812                                            | 4.18   | 88.9         |  |  |  |

| Nominal                                         | 4.7    | 100          |  |  |  |

ratings.

If we were to examine a broader range of capacitors, we would find this behavior to be common. The sample set of capacitors that I considered in my investigation did not exhibit the behavior to the same extent as the general population of ceramic capacitors would.

A third observation is that, for the same package, X7Rs have better temperature sensitivity than do X5Rs. I do not know whether this holds true universally, but it did seem so in my investigation.

Using the data from this graph, Table 2 shows how much the X7R capacitances decreased with a 12V bias. Note that there is a steady improvement with progressively larger capacitor sizes until the 1210 size; going beyond that size yields no real improvement.

### **CHOOSING THE RIGHT CAPACITOR**

In my case, I had chosen the smallest available package for a 4.7-µF X7R because size was a concern for my project. In my ignorance, I had assumed that any X7R was as effective as any other X7R; clearly, this is not the case. To get the proper performance for my application, I had to use a larger package.

I really did not want to go to a 1210 package. Fortunately, I

Figure 1 As this graphic representation of temperature variation versus dc voltage for select 4.7-µF capacitors shows, as the package size increases, the capacitance variation with applied voltage substantially decreases.

24 EDN Europe | MARCH 2013 [www.edn-europe.com]

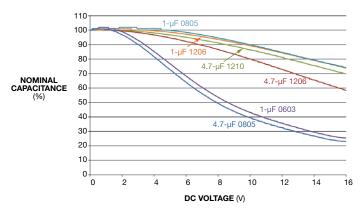

Figure 2 This graph, which plots the voltage performance of  $1-\mu F$  and  $4.7-\mu F$  capacitors, shows similar performance for the  $1-\mu F$  0603 and the  $4.7-\mu F$  0805.

had the freedom to increase the values of the resistors involved by about  $5\times$  and thereby decrease the capacitance to 1  $\mu$ F.

Figure 2 graphs the voltage behavior of several 16V, 1- $\mu$ F X7R caps versus that of 16V, 4.7- $\mu$ F X7Rs. The 0603 1- $\mu$ F capacitor behaves about the same as the 0805 4.7- $\mu$ F device. Both the 0805 and 1206 1- $\mu$ F capacitors perform slightly better than the 1210 4.7- $\mu$ F size. Thus, by using the 0805 1- $\mu$ F device, I was able to keep the capacitor size unchanged while getting a capacitor that only dropped to about 85% of nominal, rather than 30%, under bias.

But I was still confused. I had been under the impression that all X7R caps should have similar voltage coefficients because the dielectric used was the same, namely X7R. So I contacted a colleague and expert on ceramic capacitors, TDK field applications engineer Chris Burkett, who explained that there are many materials that qualify as "X7R." In fact, any material that allows a device to meet or exceed the X7R temperature characteristics,  $\pm 15\%$  over  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ , can be called X7R. Burkett also explained that there are no voltage-coefficient specifications for X7R or any other ceramic-capacitor type.

This is a critical point, so I will repeat it. A vendor can call a capacitor X7R (or X5R, or any other type) as long as the cap meets the temperature-coefficient specs, regardless of how bad the voltage coefficient is. This fact reinforces the old maxim (pun intended) that any experienced applications engineer knows: Read the data sheet!

As capacitor vendors have turned out progressively smaller components, they have had to compromise on the materials used. To get the needed volumetric efficiencies in the smaller sizes, they have had to accept poorer voltage coefficients. Of course, the more reputable manufacturers do their best to minimize the adverse effects of this trade-off.

Consequently, when using ceramic capacitors in small packages—indeed, when using any component—it is extremely important to read the data sheet. Regrettably, often the commonly available data sheets are abbreviated and will provide little of the information you'll need to make an informed decision, so you may have to press the manufacturer for more details.

What about those Y5Vs that I summarily rejected? For kicks, let's examine a common Y5V capacitor. I chose a 4.7-µF, 0603-packaged capacitor rated at 6.3V—I won't mention the

vendor, because its Y5V cap is no worse than any other vendor's Y5V cap—and looked at the specs at 5V and +85°C. At 5V, the typical capacitance is 92.9% below nominal, or 0.33 µF.

That's right. Biasing this 6.3V-rated capacitor with 5V will result in a capacitance that is 14 times smaller than nominal.

At +85°C with 0V bias, the capacitance decreases by 68.14%, from 4.7 to 1.5  $\mu F.$  Now, you might expect this to reduce the capacitance under 5V bias from 0.33 to 0.11  $\mu F.$  Fortunately, however, those two effects do not combine in this way. In this particular case, the change in capacitance with 5V bias is worse at room temperature than at +85°C.

To be clear, with this part under 0V bias, the capacitance drops from 4.7  $\mu$ F at room temperature to 1.5  $\mu$ F at +85°C, whereas under 5V bias the capacitance increases with temperature, from 0.33  $\mu$ F at room temperature to 0.39  $\mu$ F at +85°C. This result should convince you that you really need to check component specifications carefully.

### **GETTING DOWN TO SPECIFICS**

As a result of this lesson, I no longer just specify an X7R or X5R capacitor to colleagues or customers. Instead, I specify specific parts from specific vendors whose data I have checked. I also warn customers to check data when considering alternative vendors in production to ensure that they do not run into the problems I encountered.